Lo que entendi del multi-slope.

Multi slope RUN-UP!Uno de los principales problemas que tiene el dual slope es el limite del integrador. El AO tiene un limite de salida.

Analizando el dual-slope durante la entrada a la señal estas cargando el capacitor con cierta energia, pero no podes cargarlo infinitamente por el problema de antes, esta energia que cargas es desconocida para vos. Supongamos 20C

Luego aplicas una tension de referencia y medis el tiempo, con esta tension de referencia sabemos a ciencia cierta que le quitas 2C/s, entonces al tomarle 10segundos llegar al 0, sabes que son 20C que se guardaron ahi.

Y aqui es donde esta el problema, para aumentar mi resolución tengo que ser capaz de almacenar mas energia, pero mi integrador me lo limita.

Entonces lo que hago es agregarle y quitarle continuamente energia para que jamas llegue a saturar

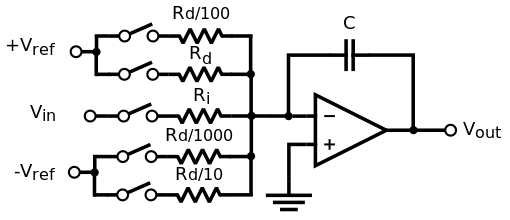

Y es lo que ves ahi. La señal de entrada siempre esta conectada,

Ahora es un sumador.

Carga desconocida + carga conocida

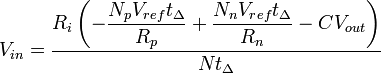

El numerador tenes. El primer termino del sumando es tu carga desconocida y las demas son las cargas que sumas/restas con la tension de referencia

Np + Nn = N

Te dice basicamente que la entrada siempre esta activa y el tiempo que esta activa es la suma del tiempo de subida y bajada de referencia.

La resultante en el tiempo de los 2 ultimos imagino que tiende a ser lo mas cercano a la entrada para que la onda crezca lo mas lento posible ( por ejemplo aplicar que baje 3V y suba 2V para una entrada de 1.2 Volt), esto te permite crear una rampa ascendente mucho mas larga. Como si fuera de 0.2V la entrada y no de 1.2V

Lo unico que podemos modificar es el tiempo de la rampa, para poder generar esa diferencia entre una y otra. Aunque conceptualmente puede estar midiendo infinitamente, como pasa en mi ejemplo que sigue.

Un ejemplo simple seria :

tengo 1C/s de entrada ( como desconocido ) mi capacitor solo soporta 20C

Mi Vref agrega 2C/s y quito 3C/s segun cual conecte

Agrego por 5 segundos. Carga total = 5C(in) + 10C(ref) = 15C

Mido.... Tengo 5C + 10C, pero se que esos 10C son agregados, entonces tengo 5C

Quito por 5 segundos. Carga total = 5C (in) + 5C (cap) - 15C (ref) = -5C

Mido.... Tenia 5C (conocido) + 5C(desconocido) - 15C(conocido) de la ref, con los 5C de antes tengo 10C en total

Agrego por 5segundos. Carga total = -5C + 10C = 5C

Quito por 5 segundos. Carga total = 5C + 5C - 15C = -5C

Si sumo la entrada trajo 20C, pero jamas llegue a mis limites

Y puedo seguir, pero si observas yo en esos 4 ciclos, logre cargar esos "20C" y no llegue jamas a mi limite del integrador en el que antes SI lo hacia y no podia cargarlo mas, asi que puedo seguir "cargandolo" infinitamente a costa de tiempo de conversion.

Aqui es donde entra la mejora de utilizar una resistencia mas pequeña de entrada permitiendo una rampa ascendete mas pronunciada y mejorar la rapidez de conversion.

Entonces es por eso que aca se ve esto:

Es una onda triangular (Con una media 0) + la carga desconocida que lo va haciendo crecer poco a poco, o una triangular montada sobre una ecuacion lineal

Como dije si el tiempo o la rampa de referencia son distintas, en algun momento las rampas van a estar por encima y cuando llegue a 0 o proximo a este en su referencia de bajada obtenemos el tiempo. Y el resto de lo que queda se medira con un ADC desde la Vout o desde el capacitor.

En este caso estamos midiendo la pendiente ascendente

RUN-DOWN!!Aqui no se trata de salvar la limitacion del integrador sino de acortar el tiempo de medicion, Como sabes en el dual-slope el ramp-up es un tiempo fijo y luego el run-down es el tiempo a conocer, entonces si tenes una entrada larga y una rampa "lenta" se tarda mucho tiempo esperando que llegue a 0.

Aqui se aprovecha del tiempo de sampleo o la histeresis del comparador.

Lo que se hace es desconectar la entrada luego del run-up y en ves de una ramapa lenta se elige la rampa mas rapida posible. Cuando cruza el 0 se abre este switch y se cambia a una rampa positiva, cruza 0 nuevamente y se cambia a negativa. Se aprovecha esa histeresis o tiempo de sampleo en el que se produce un overshoot, es decir cruza el 0 y no queda exactamente en 0. Ese overshoot es lo que hace posible este metodo.

la primer rampa es funcion de la entrada, ya que no sabemos cuanta carga habia almacenada

El overshoot MAXIMO como dije esta dado por el tiempo de sampleo y la rampa, esto va a depender de cada slope ( aplicacion de referencia con una resistencia distinta ), este caso maximo se daria que justo nuestra rampa en el sampleo anterior de justo 0.

Pero normalmente esto no ocurria, suponete de ejemplo que sampleamos a 0.1V y la rampa baja a 0.2V/s , nosotros sampleamos a 1s. entonces en el proximo sample tendriamos -0.1V , espero que con este ejemplo entendas a que me refiero de maximo.

Esa "carga" residual que nos queda, es medida con otra rampa, pero esta ves ascendente y mas lenta, ahora esta rampa tiene un tiempo o numero MAXIMO de ciclos definidos ( por eso ves en la imagen que se usan potencias de 10 en las resistencias o Base 10, se puede elegir cualquier otra base, B = 10 )

Esto hace que el numero maximo de ciclos para el slope(rampa) N sea:

Ej si N=3 y B=10, maximo numero de ciclos es de 20, es decir va a tomar 20 o menos. para esa rampa

Esta rampa nuevamente va a tener esa carga residual y asi se pasa a la otra rampa.

Entonces podemos determinar la cantidad de carga que existe

Teniendo en cuanta el numero de clock (conocido), la pendiente de cada una de las rampas (conocido) esto va a agregar y restar cargas tal como se hizo con el run-up. dando finalmente con nuestro valor.

Tension residual.Usando la formula de la mejora de Run-UP

En ves de hacer un Run-Down (o tal ves lo hace y aun asi lo mide) y asi llegar a 0 se puede leer directamente la tension del capacitor. Tomando la carga que queda y que repesenta a la entrada.

Esta analiticamente se puede obtener si despejas Vin de esa formula. O lo que seria igual a la Vin quitandole la Vin medida hasta ese momento.

En la wiki dice que como depende de todos los componentes suele agregarse una constante que afecte a C*Vout

Y despues se habla de usar ADC en el run-up para leer la carga inicial del capacitor y la final

No se si estoy tan errado pero es lo que entendi

Cualquier queja, quejarse con wikipedia o el que creo el articulo por explicarlo tan vagamente xD

Por cierto se me ha olvidado decirte que la xilinx sale al final del vídeo, en una placa a parte que se encarga del conector de vídeo, también se podría haber hecho con otro procesador mejor.

No es una salida de video.

es de una salida GPIB General-Purpose Instrumentation Bus (GP-IB) copia de Hewlett-Packard Instrument Bus (HP-IB), ahora IEEE - 488

Mi idea es que es totalmente obsoleta, PERO tal ves por temas de compatiblidad retroactiva lo sigan poniendo, y como dice en el video es opcional, lo que puede exigir la razon del por que posee una fpga aparte.